# Using an induction prover for verifying arithmetic circuits

Deepak Kapur<sup>1</sup>, M. Subramaniam<sup>2\*</sup>

<sup>1</sup> Department of Computer Science, University of New Mexico, Albuquerque, NM 87131, USA; E-mail: kapur@cs.unm.edu

<sup>2</sup> Microprocessor Division, HAL Computer Systems, Fujitsu Inc., Campbell, CA 95014, USA; E-mail: subu@hal.com

**Abstract.** We show that existing theorem proving technology can be used effectively for mechanically verifying a family of arithmetic circuits. A theorem prover implementing: (i) a decision procedure for quantifier-free Presburger arithmetic with uninterpreted function symbols; (ii) conditional rewriting; and (iii) heuristics for carefully selecting induction schemes from terminating recursive function definitions; and (iv) well integrated with backtracking, can automatically verify number-theoretic properties of parameterized and generic adders, multipliers and division circuits. This is illustrated using our theorem prover *rewrite rule laboratory* (*RRL*). To our knowledge, this is the first such demonstration of the capabilities of a theorem prover mechanizing induction.

The above features of RRL are briefly discussed using illustrations from the verification of adder, multiplier and division circuits. Extensions to the prover likely to make it even more effective for hardware verification are discussed. Furthermore, it is believed that these results are scalable, and the proposed approach is likely to be effective for other arithmetic circuits as well.

Key words: CE<sup>a</sup>

## 1 Introduction

$CE^{a}$  Please supply 5 key words.

Ever since Intel admitted to a bug in the division algorithm of its Pentium chip in November 1994, interest in the use of formal methods and tools supporting them, especially for enhancing the reliability of hardware circuits, has increased considerably both in the industry and in academia. In early 1995, we decided to try our theorem prover *rewrite rule laboratory* (*RRL*) for verifying properties of arithmetic circuits. We started with adder circuits [29], then moved on to multiplier circuits [28]. Most of this work was completed in 1995. In late 1996 and early 1997, we used *RRL* for the analysis of the SRT division circuit. The invariant properties of the SRT division circuit have been verified using *RRL* in three different ways [24, 31, 34].

In this paper, we discuss our efforts, focusing on the features of the theorem prover RRL found useful for this application. The main goal of our investigations has been to determine the extent to which a rewrite rule based theorem prover can be used to automatically verify arithmetic circuits, much like BDD-based software and the related Boolean equivalence checkers frequently used in the hardware design community. We propose some extensions to and future work on theorem provers such as RRL which would make them better suited for the application of hardware design analysis and verification.

Three classes of commonly used arithmetic circuits including adders, multipliers and divider circuits are described in this paper. The adder circuits, being the simplest, are used to illustrate the basic capabilities of RRL. Then, we show how RRL can be used to give a common specification and a fully automatic proof of an important class of multiplier circuits including several commonly used multipliers. The identification of such a class and exhibiting their commonality is one of the contributions of this paper. These circuits bring out the effectiveness of the induction and lemma generation capabilities of RRL. Finally, divider circuits illustrate the power of integration of linear arithmetic decision procedure and contextual rewriting implemented in RRL.

In the next section, we briefly outline the approach taken for verifying properties of arithmetic circuits. In the

Editor's or typesetter's annotations (will be removed before the final T<sub>E</sub>X run)

$<sup>\</sup>ast$  Partially supported by the National Science Foundation Grant no. CCR-9712366

third section, we review RRL and its capabilities. In subsequent sections, we discuss the main features of RRLfound useful for this application, using the case studies of verification of properties of various arithmetic circuits.

#### 1.1 Verification approach

Our verification attempts are quite modest and limited in the sense that we never consider real circuits or their descriptions in some well-known hardware description language. Instead, circuits are described in a functional equational language with simple data types acceptable by *RRL*. This is much in the spirit of the earlier work on  $\[cb]{eb}\]$  hardware verification using Boyer and Moore's prover and ACL2, as well as PVS work, although the language used by *RRL* is simpler in contrast to the powerful specification language of PVS, which is based on higherorder logic and syntax and allows parameterization and dependent types.

Adder and multiplier circuits in this paper are described algorithmically using recursive definitions on bit vectors (which are represented as lists of bits). Properties of these circuits are typically expressed in terms of number-theoretic properties. In the case of SRT division, we have followed the approach taken in [13], where the algorithm is given using numbers instead of bit vectors. Writing such a specification in terms of bit vectors should not add significantly to the complexity of verification process.

#### 2 Related work

Different approaches have been proposed in the literature for verifying arithmetic circuits. These can be classified into the following three main techniques: state-based techniques using BDDs and their variants and model checkers [8, 11]; induction-based techniques adapted from software verification [7, 21]; and techniques based on modeling hardware circuits using higher-order logics [12, 14]. The latter two approaches have often collectively been referred to as theorem proving based approaches. Papers on these approaches have appeared in recent conferences such as CAV and FMCAD.

These approaches have traditionally been compared and contrasted in terms of their automation capability and their expressiveness. The state-based approaches have been espoused as the most automated of the three approaches. Induction-based approaches provide some degree of automation aided by several built-in heuristics in theorem proving tools. Finally, the approaches based on higher-order logic tend to be highly interactive. Statebased approaches are typically applicable only over finite domains whereas induction-based approaches are applicable to both finite as well as unbounded domains. The approaches based on higher-order logics are the most expressive of the three.

State-based approaches based on symbolic manipulation of Boolean functions using binary decision diagrams BDDs [8] as canonical representations for Boolean functions are perhaps the most popular for verifying hardware circuits of fixed word size. A hardware circuit is specified using a Boolean function that can be succinctly represented using a *BDD*. *BDDs* provide a fast mechanism for comparing Boolean functions. Since the size of a Boolean function and hence the associated *BDD* is dependent on the word size, these approaches are well-suited for verifying non-parametric circuits. Even for linear circuits, in which the output is a linear function of the inputs, this approach has two major limitations: (i) it is unclear how circuits of arbitrary word size can be verified; and (ii) verification is limited to showing that a circuit implements a Boolean function, and not a function on numbers.

Verification of parametric (generic) descriptions of circuits has been typically carried out using theoremproving approaches. Not only is it possible to prove equivalence of Boolean functions of arbitrary word sizes, but more importantly, it is possible to verify that a Boolean function indeed implements a given number-theoretic function. Another advantage of these approaches is that a single proof suffices to establish the behavioral correctness of a generic circuit which stands for a family of circuits of different word sizes. A major criticism of the theorem proving approaches is that they are semiautomatic based on heuristics, and often require expert user guidance. This is especially so for the approaches based on higher-order logics that primarily support an interactive mode of operation.

The approach used in this paper is in the spirit of Hunt's work [21], in which circuits are described as recursive functions, and their properties proved using a theorem prover mechanizing induction. Our goal in this paper, however, has been to demonstrate how the induction-based approach can achieve a degree of automation comparable to state-based approaches for arithmetic circuit verification. We have shown how the existing rewriting technology along with induction techniques implemented in RRL can automatically discharge correctness proofs of arithmetic circuits while retaining all the advantages provided by the general framework underlying theorem provers.

The case studies performed in *RRL* are described in Table 1. All of these case studies were done on a Sparc-5 workstation with 32 Mb of memory.

We briefly review the literature on verification of adders, multipliers and division circuits in the rest of this section.

## 2.1 Adder and multiplier circuits

A linearly specified ripple carry adder where an adder of size n is recursively specified in terms of an adder of size  $CE^{c} n - 1$  has been verified by a number of theorem

CE<sup>b</sup> Please add ref cite after 'Boyer and Moore's' below. CE<sup>c</sup> Please change hyphen in line below to minus sign.

| Circuits                                                              | Definitions | Lemmas | $\operatorname{Time}(\operatorname{Secs})$ |  |

|-----------------------------------------------------------------------|-------------|--------|--------------------------------------------|--|

| Ripplecarry-Carrylookahead Adders (numeric repres.)                   | 15          | 2      | 14.00                                      |  |

| Ripplecarry(linear)-Ripplecarry (div.& conq.)Adders (numeric repres.) | 23          | 3      | 17.73                                      |  |

| Ripplecarry(linear)-Ripplecarry (div.& conq.)Adders (bit repres.)     | 21          | 3      | 14.40                                      |  |

| Ripplecarry(linear) Adder (numeric repres.)                           | 11          | 0      | 10.25                                      |  |

| Ripplecarry(linear) Adder (bit repres.)                               | 9           | 0      | 7.73                                       |  |

| CarrySave Adder (bit repres.)                                         | 7           | 0      | 6.25                                       |  |

| Linear Array Multiplier                                               | 12          | 0      | 2.48                                       |  |

| Wallace Tree Multiplier                                               | 12          | 0      | 2.45                                       |  |

| 7-3 Multiplier                                                        | 12          | 0      | 6.22                                       |  |

| Radix 4 SRT Divider (abstract table)                                  | 0           | 0      | 900                                        |  |

| Radix 4 SRT Divider (explicit table)                                  | 12          | 0      | 60                                         |  |

Table 1. Arithmetic circuit case studies in RRL

proving systems including *PVS*, *Nqthm*, *HOL*, *SPIKE-AC*, *Clam-Oyster*. However, verification efforts for the ripple-carry adder with a divide-and-conquer representation and the carry-lookahead adder have been very few, perhaps because these circuits are complex. Most verification efforts involving the carry-lookahead adder have been done in the context of verifying different forms of ALUs and processors. In [49] and [1], the verification of a parameterized ALU is reported using *Nqthm* and the *HOL* system respectively. The correctness proof described in [49] requires around 22 user-suggested intermediate lemmas to establish the correctness of the ALU with respect to addition.

In [7], Brock et al., describe the use of *Nqthm* for a comprehensive case study on the verification of the FM9001 microprocessor that includes a proof establishing the equivalence of a carry-lookahead adder and a ripple-carry adder. The proof is rather involved, using a number of built-in library functions and requires significant user intervention. In many of these proofs, the user has to explicitly provide the induction scheme.

In [29] we discussed the correctness proofs of several adder circuits including ripple-carry and carry-lookahead adders using RRL. As described in the table above, the correctness proof of the ripple-carry adder can be established automatically in RRL. The correctness of a carry-lookahead adder is done by exhibiting its equivalence to a ripple-carry adder. This requires only two intermediate lemmas. The carry-lookahead scheme used by us [29] is regular and is similar to the lookahead scheme propagate-generate scheme reported in [7].

Fixed size adder circuits are easily verified using BDDbased techniques. This is typically done by specifying both the behavior of the adders and the circuit in terms of Boolean functions and checking for the equivalence of these functions.

Unlike adder circuits, verification efforts involving multiplier circuits have been relatively few. It is well known that BDD-based techniques do not work well for multiplier circuits. Bryant and Chen introduced a new data structure *multiplicative binary moment diagram* (BMD) for modeling the functionality of circuits in terms of data at the word level [9]. Using this approach, a number of integer multiplier designs with word sizes up to 256 bits have been verified. However, such verifications are not fully automatic as stated in [9].

Our approach for verifying multiplier circuits is similar to the one suggested using BMDs in the sense that the circuit is decomposed into two components, and the number-theoretic correctness of the individual components is established. The overall proof then follows by the composition of these two components. However, the lemma generation heuristics in RRL automatically generate the required specification of these components, and the composition is also automatically done based on the circuit structure. Due to the generality afforded by theorem provers like RRL, it was also possible to obtain a common proof for a family of multiplier circuits of arbitrary size (parametric circuits) which would be infeasible otherwise.

A linear array multiplier has also been verified using the theorem prover PVS [42]. The proof is interactive and requires user guidance.

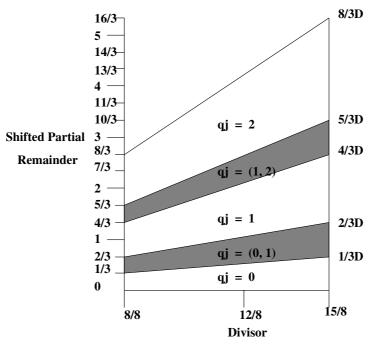

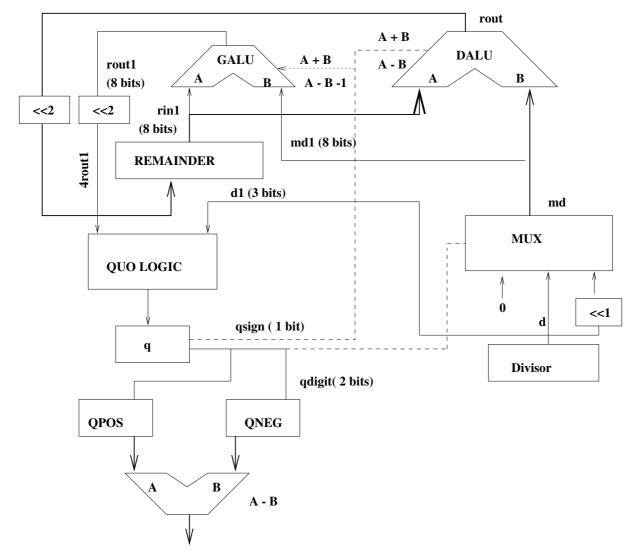

#### 2.2 Division circuits

Since Intel's Pentium bug was reported in the media, there has been a lot of interest in automated verification of the SRT divider circuits [10, 13, 19, 36, 43].

For the SRT division circuit, Bryant [10] discussed how BDDs can be used to perform a limited analysis of some of the invariants. As reported in [43], Bryant had to construct a checker-circuit much larger than the verified circuit to capture the specification of the verified circuit.

Taylor's description of the SRT division circuit has been formalized by [13, 19] using the languages of Maple, a computer algebra system, and Analytica, a prover built over Mathematica, another commercially available computer algebra system. A correctness proof of the SRT divider circuit was then done using Analytica. The main feature of the proof was an abstraction of the quotient selection table using the six boundary value predicates. This abstraction had to be manually provided. The proof

3

of invariants using this intensional representation of quotient selection table involves reasoning about inequalities, which can become quite tedious and involved. Even though it is claimed in [13] that the proof is "fully automatic" (p. 111 in [13]), the proof (especially, the proof of the second invariant regarding the boundedness of partial remainders) had to be decomposed manually and the two assumptions had to be discharged manually.

Our first proof attempt of SRT division discussed in [24] was essentially an exercise to determine how much of the Analytica proof [13] could be done automatically by *RRL* without having to use any symbolic computation algorithms of computer algebra systems. We mimicked the proof in [13] but by making data dependency of various circuit components explicit on different data paths, as well as by identifying different assumptions made in the proof reported in [13]. Much to our surprise, once we succeeded in translating the Analytica specification to RRL's equational language (which, by the way, was the most nontrivial part of this proof), RRL was able to find proofs of all the formulas (the first invariant and the second invariant with the assumptions, as well as the discharging of assumptions) automatically, without any interaction.

In [31], we gave another proof of the SRT division circuit using an explicit representation of the quotient digit selection table, thus getting rid of an aspect of the specification development where human guidance is used for abstracting table entries as predicates. Further, since the abstract representation of the quotient selection table using boundary value predicates in [13, 24] just considers the minimum and maximum values of a partial remainder for every quotient digit, thus losing information on other relations among entries, it is possible to certify erroneous tables correctly. Even though the proof using explicit table representation has nearly 1536 subcases in contrast to 96 subcases in the proof in [24], the proof of each subcase is much easier and a lot quicker to obtain, as a subformula typically involves numeric constants that can be easily simplified.

During the course of this proof, we observed that the proofs of many of the subgoals share a common structure. We have described how this commonality can be automatically exploited in the theorem prover RRL by formalizing tables as a special data type and by exploiting the sparsity of the quotient digit selection table in SRT division. This leads to a compact proof with only 12 top-level cases.

The proof reported in [36, 43] using the PVS system is more general than the above proofs of the SRT division circuit. It includes a general theory of SRT division for arbitrary radix r and an arbitrary redundant quotient digit range [-a, a]. The theory is instantiated for the radix 4 SRT division. The specification is developed with considerable human ingenuity, and the resulting proof is manually driven, even though parts of the proof can be done automatically using previously developed PVS tactics. As reported in [43], the correctness proof of the table implementation itself took 3 h of cpu time, with the whole proof taking much longer even with user's help.

Miner and Leathrum's work [36] generalizes the proof in [43] to IEEE floating point numbers and establishes the correctness of an IEEE compliant SRT division algorithm. Moore et al. [35] reported a proof of correctness of the kernel of a microcoded floating point division algorithm implemented in AMD's 5K86 processor. The proof is done ced using ACL2, a descendant of Boyer and Moore's prover. No claim is made about making the proof automatic, but rather the main emphasis is on formalizing the IEEE floating point arithmetic to verify the division algorithm based on Newton-Raphson's method.

#### 3 Rewrite rule laboratory

The theorem prover rewrite rule laboratory (RRL) supports equational and inductive reasoning using rewrite techniques. The specification language of RRL is equational, with support for defining abstract data types using constructors. RRL transforms its input into equations and conditional equations to be universally quantified. For instance, circuits and their behavioral specifications are transformed as equations and conditional equations. Definitions are distinguished from properties (lemmas) using := for definitions and == for properties to stand for the equality symbol. The correctness of circuit descriptions is established by proving various properties about these descriptions, and showing that they meet the behavioral specifications.

RRL is different in its design philosophy from most proof checkers such as PVS, HOL, Isabelle, NUPRL, LP, in the sense it attempts to perform most inferences automatically without user guidance. In this sense, it is closer in spirit to the Otter and EQP provers developed at Argonne National Laboratory. Many proofs in RRL can be generated automatically; RRL can be used in such cases as a push-button theorem prover. In fact, that is how we typically use RRL for finding proofs, starting without having any clue about how a proof can be done by hand.

RRL has built-in heuristics for:

- 1. Orienting equations into terminating rewrite rules

- 2. Identifying the next rewrite rule to apply for simplification, and for that, determining the instantiation of the free variables, and discharging conditions, if any, of the rewrite rule

- 3. Invoking decision procedures for numbers (quantifierfree Presburger arithmetic), bits, data types with free constructors, and propositional logic

- 4. Selecting the next inference rule

- 5. Automatic generation of case analysis

- 6. Choosing induction schemes based on the definitions of function symbols appearing in a conjecture and interaction among these definitions

MS ID: STTTN032 31 May 2000 14:59 CET

ce<sup>d</sup> Ref cite for Boyer and Moore.

- 7. Generating intermediate lemmas needed

- 8. Automatic backtracking to try an alternative proof attempt when one proof attempt fails.

Much like Boyer and Moore's theorem prover Nqthm [5] all the heuristics are applied in the same order using the same strategy in RRL.

The user is thus relieved of the task of having to determine the sequence in which rewrite rules should be applied, when decision procedures should be invoked, how rewrite rules should be instantiated, when induction is performed, variables to be used for induction, and what induction scheme should be used. Below, we briefly review some of these heuristics.

Each rewrite rule used by RRL must be terminating, which is ensured by an algorithm implementing a wellfounded reduction ordering, called lexicographic recursive path ordering, for comparing terms based on precedence relations among function symbols [16]. It is possible to override this feature of RRL but then there is no guarantee that simplification using manually-oriented rules terminates. Terminating rewrite rules are automatically used for simplification as well as for constructing induction schemes for mechanizing proofs by induction.

Simplification with respect to a context (called *contextual rewriting*) is the main inference mechanism used by RRL. The simplification algorithm in RRL automatically determines the applicable rewrite rule on a given conjecture. This is done by first determining the possible instantiation for the variables in the rewrite rule, and then ensuring that the conditions in the rewrite rule, if any, are satisfied. Discharging of conditions is done taking into account the context of the formula being simplified and using other rewrite rules and the decision procedures which are tightly integrated with rewriting.

*RRL* attempts to prove a conjecture by normalizing its two sides using contextual rewriting and the decision procedures for discharging any hypotheses, if any, and checking whether the normal forms of the two sides of the conjecture are identical. If it succeeds, then the proof is said to have been obtained using equational reasoning and decision procedures.

If an equation cannot be proved by simplification, then a proof by induction is attempted. Variable(s) to perform induction on **GPS** the induction scheme are automatically selected using heuristics implemented to support the *cover set* method. The definitions of function symbols appearing in a conjecture are analyzed. An induction scheme is generated from the definition of one (or more) function symbol(s) selected, based on wellfounded ordering used to establish termination of these function definitions. This scheme is often successful in determining the truth-value of the conjecture. The conjecture would be split into many cases, each corresponding to a subgoal to be proved in order to prove the original conjecture. Each subgoal is then tried just like the original conjecture. If a proof attempt based on a particular induction scheme does not lead to a counter-example, but also does not succeed, RRL automatically backtracks to pick another induction scheme (and perhaps different induction variables) for attempting the conjecture. Additional inductions may be necessary to establish the induction subgoals. The depth of permissible inductions is provided as a parameter in RRL that can be modified by the user. The proof attempt of a subgoal fails once the number of inductions exceed this depth. The number of inductions in establishing a subgoal can be iteratively increased until a diverging pattern and/or need for additional lemmas is apparent.

RRL supports a variety of heuristics for automatically generating intermediate lemmas based on formulas generated during a proof attempt. We consider the intermediate lemma speculation research to be the most critical for automating proofs by induction. RRL implements a simple heuristic for conjecture speculation by abstracting common subexpressions appearing in a conjecture to new variables using certain criteria as well as by weakening a condition in a conditional conjecture. Another heuristic found especially useful for proving properties of tail-recursive definitions (which is indeed the case for arithmetic circuits including adders and multipliers) is that of generating bridge lemmas which facilitate the use of induction hypotheses in a proof attempt of an attempted valid conjecture. A constraint-based approach is **CE**<sup>f</sup> developed to speculate about intermediate conjectures as well as guess instantiations for non-induction variables in a conjecture [30, 46]. In verifying properties of arithmetic circuits, some of the intermediate lemmas needed can be generated from the circuit structure and component specifications, as illustrated later for multiplier circuits.

Lemmas which cannot be generated automatically by RRL must be provided by the user. This is where RRL needs guidance from the user.

When a proof attempt fails and a proof cannot be found automatically, the transcript is looked at, which may reveal a variety of things. The conjecture may have to be modified, a definition may have to be fixed, or perhaps, an intermediate lemma needs to be proposed.

Below, we list the main features of RRL found useful for hardware verification. These features are illustrated in subsequent sections where different arithmetic circuits are discussed in more detail.

# 3.1 Useful features of RRL for arithmetic circuit verification

Four major features seemed to have contributed to *RRL* being effective in our mechanization attempts in verifying properties of arithmetic circuits:

1. Fast and automatic contextual rewriting and reasoning about equality

**CE<sup>e</sup>** The word 'and' eliminated in line below, OK? **CE<sup>f</sup>** The word 'about' added in line below, OK?

- 2. Decision procedures for numbers and freely built recursive data structures such as lists and sequences, and their effective integration with contextual rewriting

- 3. The cover set method for mechanization of proofs by induction, and its integration with contextual rewriting and decision procedures

- 4. Intermediate lemma speculation.

In Sect. 4 we review contextual rewriting, its interaction with decision procedures for equality on ground terms and quantifier-free theory of numbers, as well as the cover set method for mechanizing proofs by induction. A ripple-carry adder is used for illustrations.

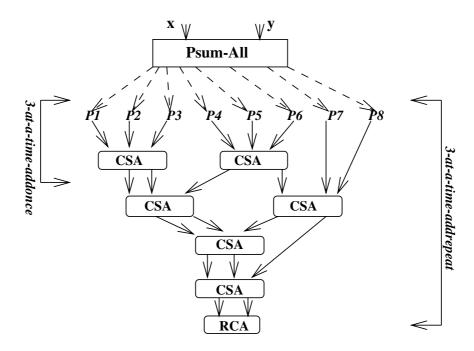

Section 5 focuses on specification and verification of a family of multiplier circuits. It discusses how a theorem prover such as RRL can be used for generic verification of a family of multipliers of arbitrary width, implementing the same generic algorithm but using components of different numbers of signals (adding a partial sum vs 3 partial sums vs 7 partial sums), and using different components realizing the same behavior.

Section 6 provides details about intermediate lemma speculation heuristics using examples from adder and multiplier circuits.

Section 7 is concerned with the handling of large tables and the extensive case analysis often needed in verifying circuits including radix-4 SRT division circuits, that use tables implemented as PLAs (programmable logic arrays).

## 4 Inference mechanisms: contextual rewriting, decision procedures, and cover-set induction

In this section, we discuss two key primitive inference mechanisms of *RRL* which turned out to be the most effective in verifying properties of arithmetic hardware circuits. We first review *simple* contextual rewriting (integrated with a decision procedure for reasoning about Horn clauses); then we show its interaction and integration with a decision procedure for equality on ground terms. Finally, it is shown how a decision procedure for a quantifier-free theory of numbers is integrated with contextual rewriting. Features/properties of a decision procedure for tight integration with conditional rewriting are described.

Later, we discuss the cover set method for generating induction schemes as implemented in RRL, and contrast it with the structural induction method. We also discuss heuristics for choosing an appropriate induction scheme.

The examples of ripple-carry adder circuits are used for illustration.

## 4.1 Contextual rewriting

Contextual rewriting is the main primitive inference in RRL. To establish a conjecture, which is typically a conditional equation (or a clause), it is first simplified with

the help of existing definitions and already proved lemmas using contextual rewriting. The proof is attempted by contradiction. The conjecture is negated and free variables are skolemized (i.e., replaced by constants). The negated conjecture, which is a conjunction of subgoals, is simplified by contextual rewriting, with an attempt to derive a contradiction in the form of a false = true or a literal conjuncted with its negation. Tautology of the form s = s is deleted from the conjunction of subgoals. Below, we show how contextual rewriting is different from rewriting.

Consider a goal, which is a conjunction of subgoals

$L_1 \wedge \cdots \wedge L_k$ ,

where each  $L_i$ , for simplicity, is either a literal of the form s = t, or (s = t) = false. A (conditional) rewrite rule

$$l \rightarrow r \ if \ cond$$

,

where *cond* is also a conjunction of literals  $c_1 \wedge \cdots \wedge c_j$ , is said to simplify the goal at subgoal  $L_i$ , to

$$L_1 \wedge \cdots \wedge L_{i-1} \wedge L_i[p \to \sigma(r)] \wedge L_{i+1} \wedge \cdots \wedge L_k,$$

if for some position p in  $L_i$ , there exists a substitution  $\sigma$  such that

- $-L_i/p^1 = \sigma(l)$ , and

- each of  $\sigma(c_m)$  (recursively) simplifies to *true* assuming the context  $L_1 \wedge \cdots \wedge L_{i-1} \wedge L_{i+1} \wedge \cdots \wedge L_k$  (i.e., every subgoal other than the subgoal  $L_i$  being simplified can be assumed to be true).

In case the rewrite rule is unconditional (i.e., there is no cond), then the above definition simplifies to checking whether the subterm of  $L_i$  at p matches the left side l of the unconditional rewrite rule.

The reason such simplification is called contextual rewriting (in contrast to rewriting) is because the remaining subgoals in the goal are used as context and are assumed to be true while determining whether the conditions of the rewrite rule are true. This is illustrated using a simple example below.

Consider a simple conditional rewrite rule

$$p(x) \rightarrow true \ if \ (q(x) \land x \neq c).$$

Given a goal

$p(a) \wedge q(a) \wedge a \neq c,$

p(a) by itself cannot be rewritten unless other subgoals in the goal are also used as its context. With the context  $\{q(a), a \neq c\}$ , p(a) can be rewritten using the above rewrite rule to *true*, simplifying the goal to  $q(a) \land a \neq c$ , since the condition of the rewrite rule is satisfied by the context.

<sup>&</sup>lt;sup>1</sup>  $L_i/p$  denotes the subterm of  $L_i$  at position p.

As the reader will notice, this is a powerful inference mechanism since it recursively involves establishing the conditions under the context surrounding the subgoal  $L_i$ . As discussed in [52], it subsumes many inference mechanisms in a first-order theorem prover based on resolution, such as demodulation, subsumption and tautology deletion. The completeness of the inference mechanism visà-vis a simplification mechanism in which the simplified goal can replace the original goal is also proved there. The power of contextual rewriting comes at a price: if some condition in *cond*, when appropriately instantiated, cannot be established (i.e., simplified to *true*), then the particular rule being considered is not applicable. So, it is important for practical applications that instantiations are not unnecessarily tried.

So far, we have discussed contextual rewriting in its simplest form. Below, we discuss how equality subgoals in a goal can be used to rewrite other subgoals, before attempting contextual rewriting on the conjecture. In a later section, we discuss how decision procedures can be integrated with contextual rewriting, using the example of quantifier-free theory of Presburger arithmetic.

#### 4.2 Role of congruence closure in contextual rewriting

In the above definition of contextual rewriting, the context of a subgoal  $L_i$  is not used to simplify  $L_i$  itself. In this sense, literals in a goal are not normalized with respect to each other. It may be the case that  $L_i$  does not match against the left side of a conditional rewrite rule, but if other equality subgoals in the context are used to rewrite  $L_i$ , then the rewritten subgoal could have a successful match. This interaction between equality reasoning and contextual rewriting can be achieved by integrating the constant congruence closure mechanism with contextual rewriting. In a later section, we show how a decision procedure for interpreted symbols other than equality can be used for normalizing a goal, much like the constant congruence closure algorithm.

Instead of checking whether  $L_i$  has a subterm at position p which matches the left side of a rewrite rule  $l \rightarrow$ r if cond, one can check whether  $L_i/p =_c \sigma(l)$ , where  $=_c$ stands for the congruence closure generated by equality literals in the context (an alternative could be some  $L'_i/p = \sigma(l)$ , where  $L'_i =_c L_i$ ). Such a check can be prohibitively expensive (it is NP-hard), so a compromise is arrived in the implementation of contextual rewriting in RRL. The equality literals in the context are used to compute a canonical rewrite system (which is equivalent to computing (ground) congruence closure generating canonical forms). The canonical rewrite system is then used to normalize  $L_i$  (as well as other subgoals in the context). If a contradiction is established this way, the goal is unsatisfiable; trivial literals of the form t = tare dropped from the normalized goal using tautology deletion. Otherwise, the normalized subgoal  $L'_i$  is then matched against the left side of a rewrite rule, as illustrated below using a simple example.

Consider again the rewrite rule discussed above:

$$p(x) \rightarrow true \ if \ (q(x) \land x \neq c).$$

Given another related goal

$$p(a) \wedge q(b) \wedge a = b \wedge a \neq c.$$

p(a) cannot be rewritten using the above rule by simple rewriting or contextual rewriting since the condition  $q(a) \wedge a \neq c$  cannot be satisfied. However, if the subgoal a = b is used to simplify the rest of the subgoals in the goal using congruence closure, we get the sightly modified goal

$$p(b) \land q(b) \land a = b \land b \neq c.$$

Using the substitution  $x \to b$  on the rewrite rule, p(b) is rewritten to *true* by contextual rewriting. The goal simplifies to:

$$true \land q(b) \land a = b \land b \neq c$$

The above analysis assumed  $a \succ b$ , but a similar analysis works if  $b \succ a$ , resulting in a different simplified goal:

$$q(a) \wedge a = b \wedge a \neq c.$$

For computing (ground) congruence closure, a simple naive algorithm for ground completion can be used; for an efficient implementation, the reader may consider Shostak's algorithm implemented as a completion procedure as described in [25]. Special care must be taken to handle equality literals of the form x = t, where x is a variable. If t does not include an occurrence of x, then this equality is oriented as  $x \to t$ , leading to elimination of x. This heuristic turns out to be very useful for simplification purposes.

# 4.3 Integration of a decision procedure with contextual rewriting

For mechanizing verification of properties of arithmetic circuits, two data structures, numbers and bit vectors, play an important role. In the previous section, it was discussed how equality on ground terms can be integrated with contextual rewriting. In this section, we discuss how to extend contextual rewriting further so that semantic information about a data structure encoded in a decision procedure can be efficiently exploited, leading to increased automation. Function symbols in the theory of the data structure being considered will be called *interpreted*, whereas other symbols are assumed to be uninterpreted.

In general, the requirements on a decision procedure for integration with contextual rewriting are:

- The decision procedure should be able to detect unsatisfiability of a quantifier-free formula with uninterpreted symbols in the theory

- Implicit equalities, if any, on terms can be deduced.

Even though the decision procedure should be sound and complete for both the requirements, an incomplete but sound procedure can still be useful.

We will illustrate this integration of a decision procedure into contextual rewriting using the example of the quantifier-free theory of Presburger arithmetic, involving 0, s, + and  $\leq, =$  for the data structure of numbers; more details can be found in [26].

Consider again a goal, which is a conjunction of subgoals  $L_1 \wedge \cdots \wedge L_k$ , with  $L_i$  being the focus subgoal being considered for simplification. It is assumed that literals in the goal include symbols of Presburger arithmetic. Recall that  $L_1 \wedge \cdots \wedge L_{i-1} \wedge L_{i+1} \cdots \wedge L_k$  serve as the context of  $L_i$ .

Above, it was shown how the context can not only be used to discharge conditions in rewrite rules used for simplification, but equality literals in the context can also be used to simplify the focused subgoal  $L_i$  using ground congruence closure. Now the decision procedure for the theory of the data structure can be used on the context to simplify the focused subgoal  $L_i$  for determining the applicability of a rewrite rule, as well as for simplification.

Using a decision procedure for a quantifier-free theory of numbers as an example, first it can be checked whether the context of  $L_i$  is unsatisfiable; if so, then the goal is unsatisfiable. Otherwise, if not, then additional equalities, if any, can be deduced using the decision procedure from the context, which can then be used by the constant congruence closure algorithm to simplify the context as well as  $L_i$ . When such simplification using the decision procedure for numbers and the constant congruence relation stabilizes (i.e., does not yield any further simplification), then rewrite rules are analyzed for possible application.

The applicability of a particular rewrite rule can be determined in two possible ways. Matching of the left side of a rewrite rule against a subterm of a subgoal can be done with respect to the theory of the data structure (also known as E-matching in the literature) which, in general, is quite expensive. An alternative is to analyze the left side of a rewrite rule and  $L_i$  to determine whether it may be useful to properly instantiate the rewrite rule for interaction with  $L_i$ . A useful heuristic is based on a wellfounded ordering on terms. If the outermost symbol of the left side of a rule is an interpreted symbol, and there is a maximal subterm of the left side that matches a subterm in  $L_i$  by a substitution  $\sigma$ , then augment the goal with the instantiation of the rule using  $\sigma$  provided the condition of the rule, when appropriately instantiated, is satisfied. Otherwise, if the outermost symbol of the left side of a rule is an uninterpreted symbol, then check for a match in  $L_i$  of the whole left side.

Suppose the following conjecture over the integers is attempted:

$$egin{aligned} & (p(x) \land (x \leq max(x,y)) \land (z \leq f(max(x,y)))) \ & \land (0 < min(x,y)) \land (max(x,y) \leq x)) \ & \supset (z < g(x) + y). \end{aligned}$$

Assume that among other rules, the following rewrite rules for max, f, g, p are already in the data base.

1.

$$min(x, y) \rightarrow y$$

if  $max(x, y) = x$ ,

2.  $f(x) \leq g(x) \rightarrow true$  if  $p(x)$ .

When the conjecture is attempted using RRL, it is first negated and skolemized to give:

$$p(A) \land (A \le max(A, B)) \land (L \le f(max(A, B))) \land (0 < min(A, B)) \land (max(A, B) \le A)) \land \neg (L < q(A) + B).$$

The resulting goal is simplified. Equality literals in the goal are used to generate a canonical rewrite system that can then be used for simplifying all literals in the subgoal. Since the only equality literal is p(A), nothing happens on this account. Now the decision procedure for numbers is invoked on the linear literals (those involving operations on numbers) to check for unsatisfiability or, if satisfiable, deducing implicit equalities. (A literal is linear if its atom is an inequality (with  $\leq$ ) or an equality.) This leads to the generation of the equality literal max(A, B) = A, which can, in turn, be used to modify the congruence relation represented as a canonical rewrite system. This in turn may further simplify the goal; in this case that indeed happens, as max(A, B) is simplified to A in other literals. The resulting subgoal, after tautology deletion (such as  $A \leq A$ ), is then:

$$p(A) \land (A = max(A, B)) \land (L \le f(A)) \land (0 < min(A, B)) \land \neg (L < g(A) + B).$$

Now rule 1 is applicable on literal (0 < min(A, B))since the condition max(A, B) = A of the instantiated rule is in the context of (0 < min(A, B)). The resulting goal is:

$$\begin{split} p(A) \wedge (A = max(A,B)) \wedge (L \leq f(A)) \wedge (0 < B) \\ \wedge \neg (L < g(A) + B) \wedge (min(A,B) = B). \end{split}$$

The new constant congruence relation, as generated by the equality literals does not lead to any simplification, nor does the arithmetic decision procedure detect any unsatisfiability or new equality literals.

Now we illustrate another interesting aspect of the integration of the decision procedure with contextual rewriting. The second rule has the linear literal  $f(x) \leq$

MS ID: STTTN032 31 May 2000 14:59 CET

CE<sup>g</sup> 'and' added in line below, OK?

g(x) (since its outermost symbol is  $\leq$ ) as its left side, in which the maximal term is  $\mathbb{CP}^{\mathfrak{S}} f(x)$ , assuming  $f \succ g$ in the precedence used to order terms for termination. The literal  $L \leq f(A)$  in the simplified goal has a subterm that can match the maximal term in the left side of a linear rule. Given that the condition of this rule can be discharged from the context, rewriting now means conjoining the literal from the instantiated rule to the goal, giving:

$$\begin{split} p(A) \wedge (A = max(A, B)) \wedge (L \leq f(A)) \wedge (0 < B) \\ \wedge \neg (L < g(A) + B) \wedge \\ (min(A, B) = B) \wedge (f(A) \leq g(A)). \end{split}$$

The arithmetic decision procedure now detects a contradiction, thus showing the goal to be unsatisfiable, implying that the original conjecture is proved from the two rules along with the theory of equality, propositional calculus and the theory of numbers. Note that without instantiating rule 2 and using it, it would not have been possible to establish the goal above, even though no instance of the left side of rule 2 appears in the original goal or its intermediate simplified forms.

The reader will notice the interaction between the congruence closure and the arithmetic decision procedure through the deduction of implicit equalities, and between the arithmetic decision procedure and rewriting for discharging conditions as well as for deducing useful instances of rewrite rules for simplification.

Rewrite rules in which the outermost symbol of the left side is a function on the data structure whose semantics is being integrated (e.g., rule 2 above) using an associated decision procedure, must be handled especially for proper/tight integration. Applicability of such rules can be tested by making weaker requirements - by requiring that the maximal subterm with an uninterpreted symbol in the left side (f(x)) in the left side of rule 2), not just the whole left side  $(f(x) \leq q(x))$ , match against a subterm (f(a)) in the conjecture. If so, the instance of the rewrite rule thus generated can be augmented for further deduction and analysis. As illustrated in the above example, the left side of the rule does not have a match in the conjecture. The instance of the rule obtained from the maximal subterm match,  $f(a) \leq g(a)$  if p(a), is simplified to  $f(a) \leq g(a)$  and added to the conjecture.

The approach for integrating a decision procedure with rewrite rules as implemented in RRL is influenced by Boyer and Moore's work [4] in integrating Fourier's decision procedure in their prover. The main distinction is that whereas Boyer and Moore convert linear equalities into a conjunction of inequalities, equalities are kept as they are. Additional equalities are deduced from linear inequalities, if any, so that they can be used as rewrite rules for discharging hypotheses/conditions in conditional rewrite rules using ground completion implementing the congruence closure. Even though the procedure for checking unsatisfiability of linear inequalities over integers (as well as for deducing equalities) is incomplete, it has been found quite effective in using *RRL* for mechanical verification of arithmetic circuits.

## 4.4 Mechanizing induction

One major distinction between the use of RRL and BDDbased tools for verifying properties of arithmetic circuits is that RRL can be used to verify properties of circuits of arbitrary widths. This is in contrast to BDD-based approaches where proofs of only fixed data path widths can be done. Even for similar circuits with different data path widths, proofs must be redone using BDD-based tools as these circuits represent different Boolean formulas and hence have different behavior. In contrast, a proof by induction in RRL can handle a potentially unbounded family of related circuits in one shot.

Unlike control dominated hardware circuits, the behavior of arithmetic circuits can generally be succinctly expressed in terms of number-theoretic properties. Such properties are typically established using induction. In contrast, in BDD-based tools, the properties of arithmetic circuits are expressed using Boolean functions. The correctness of the circuit is established by exhibiting the input-output behavioral equivalence of the two Boolean functions – one representing the circuit and the other representing the property.

Methods for mechanizing induction thus play a critical role in automatically proving number-theoretic properties of arbitrary width arithmetic circuits. In this section, we review the cover set induction method, the main technique for generating induction schemes in *RRL*. We discuss how induction schemes are automatically generated from terminating function definitions. This is illustrated by proving number-theoretic properties of an arbitrary width ripple-carry adder circuit. Later we discuss heuristics implemented in the theorem prover for choosing an appropriate induction scheme, and contrast the cover set induction approach with the structural induction method.

#### Cover set induction method

A proof of a given conjecture of the form l = r if cond, is always first equationally attempted in RRL by contextual rewriting and decision procedures. If a conjecture cannot be established or refuted by equational reasoning, then RRL automatically attempts to prove the simplified conjecture by induction.

RRL uses the cover set induction method for automating well-founded induction. The cover set method was proposed in [53], and it has been successfully used to prove many nontrivial theorems by induction on numbers, lists, arrays and other recursive data structures. Along with contextual rewriting, this is another powerful inference mechanism supported in RRL.

In contrast to structural induction, there is no fixed inductive inference rule for a data type in the cover set induction approach. Different function definitions on the same data type can lead to different inductive inference rules for the same data type.

The cover set method automatically generates induction schemes for a given conjecture. The induction schemes are generated using complete definitions of functions given as terminating rewrite rules. The induction subgoals are automatically generated from the induction scheme. We describe the main steps of the cover set induction method below:

1. Generating cover sets from terminating function definitions: the definitions of function symbols are first preprocessed by *RRL*, oriented into terminating rules and are analyzed for completeness using several builtin heuristics. A cover set is generated from each complete terminating function definition.

A cover set associated with a definition of a function f is a finite set of triples. There is one triple for each rule in the definition. The first element of the triple is derived from the left-hand side of the rule. The second element of the triple is a set whose elements are derived from the recursive calls to fon the right-hand side of the rule. The last element of the triple is derived from the conditions governing the rule. For a rule  $l \to r$  if cond, where l = $f(s_1, \dots, s_n)$  and  $f(s_1^i, \dots, s_n^i)$  is the *i*<sup>th</sup> recursive call to f in the right side r, the corresponding triple is  $\langle \langle s_1, \dots, s_n \rangle, \{\dots, \langle s_1^i, \dots, s_n^i \rangle, \dots \}, cond \rangle$ .

The second and the third components of a cover set triple are the empty set if there is no recursive call to f in r and if there is no condition *cond* associated with the rule.

2. Generating subgoals using induction schemes: an induction scheme is generated from a term  $f(x_1, \dots, x_n)$ appearing in the conjecture using the cover set of f. An induction scheme is a finite set of induction cases. There is one induction induction case corresponding to each cover set triple. Each induction case generates an induction subgoal which must be established in order to prove the given conjecture. Each induction case is a triple whose elements are generated from the corresponding elements in the cover set triple. The first element of the triple is the substitution  $\sigma_c$ , the second element is the set of substitutions  $\{\theta_i\}$  and the last element is the condition governing the induction subgoal  $cond_c$ . The substitution  $\sigma_c$  is used to generate the induction conclusion of the induction subgoal, each substitution in  $\{\theta_i\}$  is used to generate an induction hypothesis for the subgoal.

For an induction scheme based on a cover set to be sound, a cover set must have two properties. First, it must be complete i.e., for each induction variable, all possible values of a data type must be considered. Second, in the induction step, the substitutions for generating induction hypotheses must be lower in a well-founded order than the substitutions in the conclusion. The second property is automatically ensured in RRL since induction schemes are generated from terminating definitions. To ensure the first property, RRL supports algorithms for checking completeness of function definitions given as terminating rewrite rules.

The cover set method has been extensively used in all our arithmetic circuit verification efforts. The working of the cover set method on a simple example of a parameterized *ripple-carry* adder is described in detail below.

## Specifying a ripple-carry adder

A ripple-carry adder is a simple hardware circuit that implements the conventional method of adding two binary numbers. The inputs to a ripple-carry adder of size n are two bit vectors of size n and an initial carry bit. The outputs is a bit vector of size n + 1. Bits are added one by one from the least significant to the most significant, with the carry from the previous stage as input, and carry output at the current stage to serve as the input to the next stage.

Bit vectors can be modeled in RRL by using lists *freely* constructed with *nil* and *cons*. The elements of lists are bits modeled in RRL by an enumerated type with constructors 0 and 1.

A parameterized ripple-carry adder using lists can be specified in RRL as follows:

- 1. rca(x, nil, nil) := cons(x, nil), 2. rca(x,cons(y1,nil),cons(z1,nil)) := cons(mod2(x,y1,z1), cons(half(x,y1,z1),nil)), 3. rca(x,cons(y1,y),cons(z1,z)) := cons(mod2(x,y1,z1), rca(half(x,y1,z1), y, z))

- if {len(y) = len(z), not(y = nil), not(z = nil)}.

The first equation defines a ripple-carry adder of size 0 to be a wire propagating the input carry bit. The output carry bit is tied to value 0. The second equation defines a ripple-carry adder of size 1 to be a full adder. A full adder takes three bits as inputs and produces a lists with two bits as its output. The first bit in the list corresponds to the sum obtained by adding the three input bits. The other corresponds to the carry obtained by the addition. The function mod2 in the equation is an abbreviation for the sum computation of a full adder. It stands  $ce^{h}$  for the bit-level operation xor. The function half is an abbreviation for the carry computation of a full adder. half(x, x1, x2) stands for the bit-level operation (x and x1) or (x and x2) or (x1 and x2).

The third equation defines an adder of size n recursively in terms of an adder of size n - 1 cascaded with a full adder. The full adder is used for adding the initial carry bit with the least significant bits of the two input bit vectors. The carry bit from the full adder is taken to be the initial carry bit for the ripple-carry adder of size n - 1. The function len above computes the length of a list.

These equations are oriented into terminating rules using lexicographic recursive path ordering implemented in *RRL*. By associating a right-left status with the function symbol rca (i.e., using a lexicographic ordering from right to left among the arguments of the function symbol rca), the recursive call rca(half(x, y1, z1), y, z) is smaller than the left-hand side rca(x, cons(y1, y), cons(z1, z)) in a well-founded order on terms induced by a precedence relation on function symbols. A cover set is generated from the above definition of rca, which is then used to generate an induction scheme for conjectures in which rca appears. Induction hypotheses are generated from the smaller recursive call to rca on the right side of the definition.

#### Showing that ripple-carry adder implements addition

A proof of correctness of the ripple-carry adder rca (i.e., rca implements addition on bit representation of numbers) is mechanically generated by RRL. It is demonstrated that given any two bit vectors y and z and an initial carry bit x, the natural number derived from the output pair obtained as a result of the ripple carry addition of x and the bit vectors y and z is the same as the sum of the numbers corresponding to y and z along with x. A functions bton is defined to convert linear lists of bits into numbers.

bton(nil) := 0, bton(cons(x, y)) := x + (2 \* bton(y)).

Note that the bit  $\mathbf{x}$  is overloaded and treated as a number in the above definition. Such overloading of bits and numbers is assumed in other function definitions as well.

The theorem expressing the correctness of the ripplecarry adder is:

```

C1: x + bton(y) + bton(z) == bton(rca(x, y, z))

if len(y) = len(z),

```

where + is addition on natural numbers.

The theorem C1 is first attempted by RRL using equational reasoning using contextual rewriting and the linear arithmetic decision procedure. Since C1 cannot be established equationally, RRL automatically invokes the cover set induction to prove C1.

The cover sets for all the non-constructor function symbols are precomputed by *RRL*. In this case, *RRL* precomputes the cover sets of the function symbols +, len, bton, rca. For example, the cover set that is precomputed for the function symbol rca is

```

[<<x, nil, nil>, {}, {}>,

<<x, cons(y, nil)>, cons(z, nil>>, {}, {}>,

<<x, cons(y1, y), cons(z1, z)>,

{<half(x, y1, z1), y, z>},

{len(cons(y1, y)) = len(cons(z1, z)),

not(y = nil), not(z = nil)}>].

```

```

CE<sup>1</sup> Could the word 'proved' be substituted with 'tested for'in line below? Alternatively, another option might be '..for all the values for which the formula..'above.

CE<sup>j</sup> 'are' added to line below. OK?

```

The first two triples above are derived from the first two equations defining rca for the empty and singleton bit vector inputs. The last triple is derived from the third equation defining rca recursively for bit vectors of size greater than 1. The first component of this triple comes from the left side of the equation. The second component is derived from the recursive call to rca on the right side, and the third component is derived from the condition in third equation. The second component of the cover set triple records distinct recursive calls.

In order to perform an inductive proof of C1, one of the function symbols +, len, bton, rca appearing in C1 is chosen. In this case, the heuristics in *RRL* pick the function symbol rca to perform induction.

The rewrite rule for **rca** defines **rca** for all the values that the formula C1 is being **cc**<sup>1</sup> proved (arbitrary carry bit and equal length bit vectors)<sup>2</sup>.

The induction scheme for C1 is automatically generated by RRL from the subterm rca(x, y, z) in C1 by using the cover set of rca:

```

Let P(x, y, z) be

bton(rca(x, y, z)) == (x + bton(y) + bton(z))

if {len(y) = len(z)}

```

```

Induction will be done on x, y, z in rca(x, y, z),

with the scheme:

[1] P(x, nil, nil).

[2] P(x, cons(x1, nil), cons(x2, nil)).

[3] P(x, cons(y1, y), cons(z1, z))

if {(len(y) = len(z), not(y = nil),

not(z = nil)),

P(half((x, y1, z1)), y, z)}.

```

Three induction subgoals are generated based on this scheme. The first two subgoals correspond to the base cases and the third goal is the induction step case. The first induction subgoal,

```

[1] bton(rca(x, nil, nil)) == x + bton(nil) +

bton(nil) if {len(nil) = len(nil)},

```

reduces to true by the definitions of the function symbols bton, rca and len.

The second subgoal,

[2] bton(rca(x,cons(x1,nil),cons(x2, nil))) ==

x + bton(cons(x1,nil)) + bton(cons(x2,nil))

if {len(cons(x1,nil)) = len(cons(x2,nil))},

simplifies by the definitions of rca, len and bton to: mod2(x, x1, x2) + half(x, x1, x2) + half(x, x1, x2) == x + x1 + x2.

This subgoal is proved by RRL by case analysis on the values of the variables x, x1, x2.

<sup>&</sup>lt;sup>2</sup> Note that rca is not completely defined for all possible input combinations. The equations define only cases where the bit  $c_{E}$  vectors are of equal lengths. In such cases the cover set induction method requires the C1 to be relativized to be proved only over defined values [27]. The condition len(y) = len(z) in C1 provides such a relativization.

The third subgoal [3] is

```

[3] bton(rca(x,cons(y1,y),cons(z1,z))) ==

x + bton(cons(y1,y)) + bton(cons(z1,z))) if

{(len(cons(y1, y)) = len(cons(z1, z))),

not(y = nil), not(z = nil),

(bton(rca(half(x, y1, z1), y, z)) =

(half(x, y1, z1) + bton(cons(y1, y)) +

bton(cons(z1, z)))) if len(y) = len(z)}

```

This subgoal is split into two intermediate subgoals by contextual rewriting based on the combination of the clauses. One of the intermediate subgoals generated is

[3.1] bton(rca(x,cons(y1,y),cons(z1,z))) ==

x + bton(cons(y1,y))+bton(cons(z1,z)) if

{len(cons(y1, y)) = len(cons(z1, z),

not(y = nil), not(z = nil),

not(len(y) = len(z))}.

Contextual rewriting of this subgoal with the definition of len combined with the linear arithmetic procedure, for the freeness of the successor function on numbers, gives conditions len(y) = len(z) and not(len(y) = len(z)). The subgoal is vacuously true due to contradictory conditions.

The other subgoal generated from [3] is

[3.2] bton(rca(x,cons(y1,y),cons(z1,z))) ==

x + bton(cons(y1,y))+bton(cons(z1,z)) if

{len(cons(y1,y)) = len(cons(z1,z)),

not(y = nil), not(z = nil),

bton(rca(half((x,y1,z1)),y,z)) =

bton(y) + bton(z) + half(x, y1,z1))}

Note that the body of the above formula corresponds to the induction conclusion and the final conjunct in the condition corresponds to the induction hypothesis. The conclusion is simplified by the definition of rca and bton to,

```

[3.2.1] mod2(x, y1, z1) +

2 * bton(rca(half(x, y1, z1), y, z) ==

x + y1 + 2 * bton(y) + z1 + 2 * bton(z)

if {len(y) = len(z), not(y = nil),

not(z = nil)}

```

to which the hypothesis can be applied. The resulting formula

is simplified by RRL by using linear arithmetic decision procedure to,

[3.2.1.1.1] mod2(x, y1, z1) + half(x, y1, z1) +

half(x, y1, z1) == x + y1 + z1

if {len(y) = len(z), not(y = nil),

not(z = nil)},

which is proved by case analysis on the variables x, y1, z1. The conditions in the above formula are actually dropped by RRL since none of the variables in the conditions occur in the body<sup>3</sup>.

All of the above steps in proving the formula [3.2] are done using the combination of contextual rewriting and the arithmetic decision procedure. Application of the hypothesis is treated just like another instance of contextual rewriting. A single application of contextual rewriting integrated with the arithmetic procedure produces the formula [3.2.1.1.1] directly from the subgoal [3.2].

#### $Choosing \ an \ appropriate \ induction \ scheme$

The choice of an appropriate induction scheme is important for the success of a proof attempt by induction. For a given conjecture, there are many possible alternative induction schemes, corresponding to function symbols appearing in the conjecture. Further, a particular function symbol may appear more than once in a given conjecture with different variables as arguments. A choice among these subterms corresponds to choosing different induction variables and leads to different subgoals.

For instance, for the conjecture C1,

```

x + bton(y) + bton(z) == bton(rca(x, y, z))

if len(y) = len(z).

```

There are three possible induction schemes based on the function symbols bton, len and rca. For the schemes based on len and bton either y or z could be chosen as the induction variable. The induction scheme based on rca uniquely determines both y and z as induction variables. A proof of C1 using the induction scheme suggested by the function symbol rca was described in the previous section.

Below, we first describe how the choice of the other alternative induction schemes leads to unsuccessful proof attempts. Then, we describe how such failures are avoided by the heuristics implemented RRL for choosing the most appropriate induction scheme and induction variables.

Consider proving C1 using the induction scheme suggested by bton with y as the induction variable. Two induction subgoals are generated for y = nil and y = cons(u1, u).

The base case with y = nil simplifies to

```

C1.1: x + bton(z) == bton(rca(x, nil, z))

if len(z) = 0.

```

Since no further simplification is possible by contextual rewriting and/or the decision procedures, the proof attempt does not succeed.

In such a case, the formula is treated as an intermediate conjecture by RRL, and an inductive proof of this

$<sup>^3\,</sup>$  This is one form of generalization that RRL supports. Generalization and other forms of intermediate lemma generation support in RRL are discussed in detail in the next section.

intermediate conjecture is attempted. An inductive proof of C1.1 could be performed based on schemes derived from the function symbols bton or len with the induction variable being z. An induction proof attempt based on the function symbol bton leads to two subgoals with z = nil and z = cons(v1, v)).

The base case with z = nil simplifies to

```

x == bton(rca(x, nil, nil)).

```

The above formula is reduced to true by the definitions of rca, bton.

The induction step case with z = cons(v1, v) is easily established since the condition 0 = len(cons(v1, v)) reduces to false using the definition of len and the linear arithmetic decision procedure.

The formula C1.1 is thus an inductive theorem. Such intermediate inductive theorems are oriented into rules by RRL, and are added to  $CE^k$  the rule database. These rules are used by RRL in subsequent as well other subgoals of the same proof. This is one way intermediate lemmas are generated, proved and stored by RRL. For further details on intermediate lemma generation, the reader can refer to the next section.

Coming back to the proof of C1, we now consider the induction step case generated based on the induction scheme based on the function symbol **bton** with the induction variable y.

In the step case, the conclusion with y = cons(u1, u) is,

x + bton(cons(u1,u)) + bton(z) == bton(rca(x,cons(u1,u),z)) if len(cons(u1,u)) = len(z),

with the hypothesis being,

```

x + bton(u) + bton(z) == bton(rca(x, u, z))

if len(u) = len(z),

```

The conclusion cannot be simplified any further. Thus the induction step case cannot be established by equational reasoning.

As done for the base case, an inductive proof of the step case can be attempted based on a scheme suggested by the function symbol **bton** with the induction variable z. Two subgoals are generated with z = nil, z = cons(v1, v).

The base case with z = nil is reduced to true due to contradictory conditions involving len. In the step case, the conclusion is

```

x + bton(cons(u1,u)) + bton(cons(v1,v)) ==

bton(rca(x,cons(u1,u),cons(v1,v)))

if {len(cons(u1, u)) = len(cons(v1, v)),

(x + bton(u) + bton(cons(v1,v)) =

bton(rca(x,u,cons(v1,v))) if

len(u) = len(cons(v1,v)))},

```

with the hypothesis being

CE<sup>k</sup> Would the word 'subgoals' be appropriate after 'subsequent' in line below?

x + bton(cons(u1, u)) + bton(v) == bton(rca(x, cons(u1, u), v)) if {len(cons(u1, u)) = len(v), (x + bton(u) + bton(v) = bton(rca(x, u, v)) if len(u) = len(v)}.

The conclusion cannot be simplified any further<sup>4</sup>. Additional inductions based on the scheme bton are not likely to help either. So, the induction proof attempt of C1.1. based on the scheme suggested by the function symbol bton fails.

An induction proof attempt based on a scheme suggested by the function symbol len similarly fails as well.

To avoid such failures it is necessary that the heuristics in RRL choose the most appropriate induction scheme suggested by rca for the conjecture C1. RRLautomatically backtracks whenever an induction proof attempt based on a scheme fails. The conjecture is retried with a different induction scheme. Attempts at proving a conjecture are abandoned by RRL once all the available schemes have been tried or at a user request.

#### Heuristics for choosing an induction scheme

Several heuristics are implemented in RRL to choose the most appropriate induction scheme from the given possible schemes. These are based on the heuristics developed for the prover Nqthm, described in [3]. Two heuristics that are frequently employed in the verification of arithmetic circuits are *subsumption* and *merging*.

Subsumption chooses an induction scheme with a common set of induction variables. An induction scheme  $\phi$ subsumes an induction scheme  $\psi$  if the substitutions for the induction variables in  $\phi$  refine those in  $\psi$ . For example, the induction scheme suggested by **rca** subsumes that suggested by **bton**, len with respect to the induction variable y or the induction variable z. The function **rca** is defined in terms of bit vectors of size 0, 1 and those with size greater than 1 whereas the functions **bton** and len are defined in terms of bit vectors of size 0 and those with size greater than 0.

If a scheme  $\phi$  subsumes a scheme  $\psi$ , the heuristics in *RRL* always choose the scheme  $\phi$ . This is because choosing a scheme  $\psi$  leads to an induction case whose conclusion cannot be simplified using the definitions since the rules are more refined than the conclusion, and hence will not match the conclusion. We describe below how the scheme suggested by **rca** is chosen by these heuristics while proving the conjecture **C1**.

A proof attempt of C1 based on the scheme suggested by bton or len fails for this reason. The subterm rca(x, cons(u1, u), cons(v1, v)) cannot be simplified by the definition of rca as the rules in the definition are further

<sup>&</sup>lt;sup>4</sup> Note that the third equation in the definition of rca cannot be applied to the conclusion. In order to apply this rule, it is necessary that not(u = nil) and not(v = nil). These conditions do not follow from the assumptions of the step case.

refined based on u and v. The case of u = v = nil is covered by the second rule and the third rule covers the case when these variables are not nil.

Using the subsumption heuristic, the schemes suggested by **bton** and **len** is discarded by RRL in favor of the scheme suggested by **rca**. This leads to a successful proof of the conjecture C1 without backtracking.

Another heuristic implemented in RRL to pick an induction scheme is *merging*. Often the induction schemes suggested by the various subterms of a given conjecture share induction variables amongst each other. An inductive proof attempt of the conjecture based on one of these schemes only is not likely to succeed in such cases. For instance, if  $t_1 = f(x, y)$  and  $t_2 = g(z, x)$  are two subterms of a given conjecture where f and g are binary functions defined recursively on both of their arguments, then attempting a proof of the conjecture by induction based only on the scheme suggested by the term  $t_1$  would result in an induction step with the conclusion containing  $t'_1 = \sigma(f(x, y)) = f(\sigma(x), \sigma(y))$  and  $t'_2 = \sigma(g(z, x)) =$  $g(z, \sigma(x))$ . The choice of induction scheme ensures that the term  $t'_1$  can be simplified to match the induction hypothesis, but the same need not be true for the term  $t'_2$ since the variable z in  $t'_2$  does not get instantiated.

In such cases, the two competing induction schemes are merged into a single induction scheme that instantiates the induction variables simultaneously in all the terms. Merging reduces the number of alternative induction schemes, and also eliminates the need to arbitrarily choose from among competing schemes.

#### Coverset induction vs structural induction

In the cover set induction method, induction schemes are generated from the definitions of nonconstructor function symbols rather than being based on the constructors of the data type. Thus, different schemes can be generated for the same data type using the cover set method. Such schemes can involve nonconstructor symbols and can differ in the induction hypotheses to be used. In contrast, there is only one induction scheme corresponding to a data type in structural induction. In the cover set induction approach, each recursive call in the definition of a nonconstructor produces an inductive hypothesis, whereas only one induction hypothesis is generated by the structural induction approach. The capability of generating multiple induction schemes and additional hypotheses seems very beneficial in verifying properties of arithmetic circuits as discussed below.

Consider a ripple-carry adder rcp based on a divideand-conquer representation. In this case, a ripple carryadder of size n is recursively defined in terms of adders of size n/2. A divide-and-conquer representation of a ripplecarry adder is often used in hardware designs [39, 40] to construct arithmetic circuits of larger data widths by cascading similar smaller data width components. Smaller data width adders are often used as standard cells in industrial ASIC designs, and logic synthesis tools often provide these in their technology libraries.

A divide-and-conquer representation of a ripple-carry adder rcp can be used to exhibit the input-output equivalence of a ripple-carry and a carry-lookahead adder, which is much easier to specify using the divide-and-conquer strategy. We have found that such an equivalence proof is more easily done than the one in which a linear representation of the ripple-carry adder rca is used. The verification proofs of ripple-carry and carry-lookahead adders are discussed in more detail in [29]. Below, we illustrate how properties of a ripple-carry adder defined using the divide-and-conquer strategy can be verified easily using the cover set method, whereas proving these properties using structural induction is nontrivial.

The adder rcp can be specified in RRL as follows:

```

1. rcp(x, nil, nil) := cons(x, nil),

```

```

2. rcp(x,cons(y1,nil),cons(z1,nil)) :=

cons(mod2(x, y1, z1),

```

cons(half(x, y1, z1), nil)),

3. rcp(x,app(y1,y2),app(z1,z2)) :=

app(sum(rcp(x, y1, z1)),

rcp(carry(rcp(x,y1,z1),y2,z2)

if {len(y1) = len(z1),

len(z1) = len(y2), len(y2) = len(z2)}.

The first two equations defining rcp are identical to those defining rca. In the third equation, there are two recursive calls to rcp on the right side. The first adder performs addition of the corresponding lower halves of the input bit vectors and the second adder performs the addition of the upper halves. The function app denotes the appending of lists, and can be recursively defined in *RRL*. The functions sum, carry denote the outputs sum and carry of the first adder. The function sum is defined recursively as a list with the last element removed. The function carry is cel defined recursively as the last element of a list.

The behavioral correctness of rcp can be stated in RRL as follows:

C2: bton(rcp(x, y, z)) == x + bton(y) + bton(z)if len(y) = len(z).

An inductive proof attempt of C2 by structural induction over lists with induction variables y, z does not seem feasible. Such a proof attempt leads to two subgoals as before. The base case with y = nil, z = nil simplifies to true by contextual rewriting.

In the step case, the conclusion with y = cons(u1, u), z = cons(v1, v) is

```

bton(rcp(x,cons(u1,u),cons(v1,v))) ==

x + bton(cons(u1,u)) + bton(cons(v1,v)) if

(len(cons(u1, u)) = len(cons(v1, v))),

```

with the hypothesis being,

bton(rcp(x, u, v)) == x + bton(u) + bton(v)if len(u) = len(v).

The conclusion cannot be simplified as there is no rewrite that can match **rcp** whose second and third arguments are **cons** terms. The hypothesis cannot be applied to the conclusion, and therefore, the proof attempt fails. Additional inductions and/or case analysis are not likely to help in this case.

C2 can, however, be established in RRL by the cover set induction scheme generated from the definition of rcp. Three subgoals are generated corresponding to the three equations in the definition of rcp. The first two equations lead to base cases, and are proved by contextual rewriting and case analysis as done for the conjecture C1. In the third subgoal, the conclusion is

[3] bton(rcp(x,app(y1,y2),app(z1,z2))) ==

x + bton(app(y1,y2)) + bton(app(z1,z2)) if

{(len(app(y1, y2)) = len(app(z1, z2)),

len(y1) = len(y2), len(y2) = len(z1),

len(z1) = len(z2))}.

Two hypotheses are generated by the cover set method from the two recursive calls of **rcp**. These are:

```

Hyp 1: bton(rcp(x, y1, z1)) ==

x + bton(y1) + bton(z2) if

{(len(y1) = len(y2), len(y2) = len(z1),

len(z1) = len(z2))}.

Hyp 2: bton(rcp(carry(rcp(x,y1,z1)),y2,z2)) ==

carry(rcp(x,y1,z1)) + bton(y2) + bton(z2)

if {(len(y1) = len(y2), len(y2) = len(z1),

len(z1) = len(z2))}.

```

Sixteen intermediate subgoals are generated by contextual rewriting corresponding to the each of the 5 clauses in the two hypotheses. 15 of these are established by contextual rewriting combined with the linear arithmetic decision procedure due to contradictory conditions over the function len.

The only remaining subgoal is

```

[3.16] bton(rcp(x,app(y1,y2),app(z1,z2))) ==

x + bton(app(y1,y2)) + bton(app(z1,z2))

if {len(app(y1,y2)) = len(app(z1,z2)),

len(y1) = len(y2), len(y2) = len(z1),

len(z1) = len(z2),

bton(rcp(x,y1,z1)) =

x + bton(y1) + bton(z2),